#### Is Now Part of

## ON Semiconductor®

To learn more about ON Semiconductor, please visit our website at <a href="https://www.onsemi.com">www.onsemi.com</a>

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA Class 3 medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, emplo

# **High Performance 100V Bridge Power Stage Module**

The 100V Bridge Power Stage (BPS) Module is a fully optimized, compact, integrated MOSFET plus driver power stage solutions for high current DC-DC switching applications. The FDMF8811 integrates a driver IC, two power MOSFETs and a bootstrap diode into a thermally enhanced, compact 6.0 mm x 7.5 mm PQFN package. The PQFN packaging ensures low package resistance improving the current handling capability and performance of the part.

With an integrated approach, the complete switching power stage is optimized with regards to driver and MOSFET dynamic performance, system parasitic inductance, and Power MOSFET R<sub>DS(ON)</sub>. The FDMF8811 uses high performance PowerTrench<sup>TM</sup> MOSFET technology, which reduces switch ringing in converter applications. The driver IC features low delay time and matched PWM input propagation delays, which further enhance the performance of the part.

#### **Features**

- Compact size 6.0 mm x7.5 mm PQFN

- High current handling: 20A

- >97% system efficiency at 600W full bridge applications PSRR value

- Wide driver power supply range: 8V to 14V

- Internal pull-down resistors for PWM inputs (HI,LI)

- 3.3V/TTL compatible input thresholds

- Short PWM propagation delays

- Drive power supply Under-voltage lockout (UVLO)

- Integrated 100V Half-Bridge gate driver with 10hm Bootstrap diode

- Low Inductance and low resistance packaging for minimal operating lower losses

- 100V PowerTrench® MOSFETs for clean switching waveforms

#### **Typical Applications**

- Telecom Half / full Bridge DC-DC converters

- Two-Switch Forward Converters

- Intermediate Bus Converters

- Brick Converters

- High-current DC-DC Point of Load (POL) converters.

## ON Semiconductor®

www.onsemi.com

#### PACKAGE PICTURE

**MARKING**

36 Lead PQFN

D=Assembly Plant Code

G= Year Code

WW=Work Week

AA= Lot Code

FDMF8811= Specific Device Code

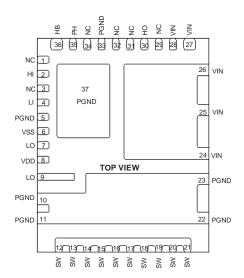

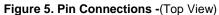

#### **Pin Connections**

#### ORDERING INFORMATION

See detailed ordering and shipping information in the package dimensions section on page 13 of this data sheet.

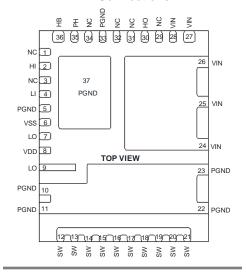

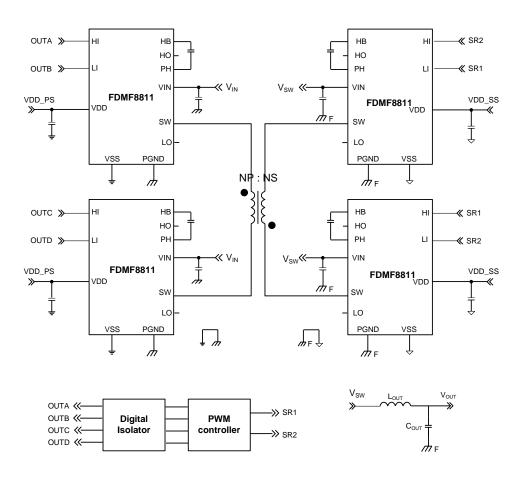

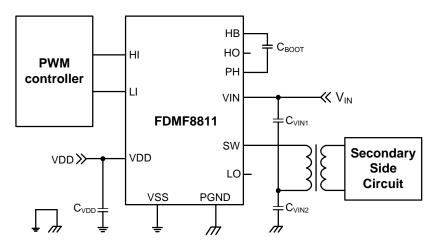

## **Typical Applications**

Figure 1. Full-Bridge Isolated DC-DC Converter

Figure 2. Typical applications in Buck DC-DC Converter

Figure 3. Half-Bridge Isolated DC-DC Converter

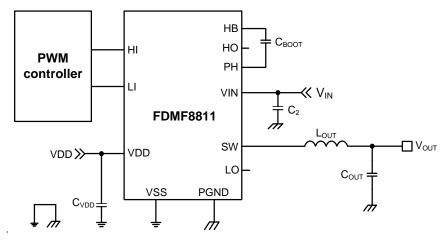

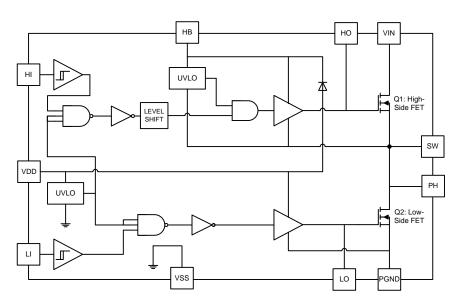

## **Block Diagram**

Figure 4. Simplified Block Diagram

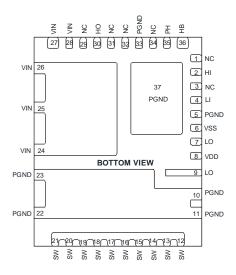

#### **PIN CONNECTIONS**

Figure 6. Pin Connections – (Bottom View)

## PIN FUNCTION DESCRIPTION

| Pin No.                      | Pin Name | Description                                                                                                             |  |  |

|------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------|--|--|

| 1, 3, 29,31-32,<br>34        | NC       | No connect                                                                                                              |  |  |

| 2                            | HI       | High-side PWM input.                                                                                                    |  |  |

| 4                            |          | Low-side PWM input.                                                                                                     |  |  |

| 5, 10, 11, 22, 23,<br>33, 37 | PGND     | Power return for the power stage.                                                                                       |  |  |

| 6                            | VSS      | Analog ground for driver IC analog circuits.                                                                            |  |  |

| 7, 9                         | LO       | Low-side gate drive output.                                                                                             |  |  |

| 8                            | VDD      | Power supply input for low-side gate drive and bootstrap diode. Bypass this pin to PGND with a low impedance capacitor. |  |  |

| 12-21                        | SW       | Switching node junction between high-side and Low-side MOSFETs.                                                         |  |  |

| 24-28                        | VIN      | Power input for the power stage. Bypass this pin to PGND with low impedance capacitor.                                  |  |  |

| 35                           | PH       | High-side source connection (SW node) for the bootstrap capacitor.                                                      |  |  |

| 30                           | НО       | High-side gate drive output.                                                                                            |  |  |

| 36                           | НВ       | Bootstrap supply for high-side driver. Bypass this pin to PH with low impedance capacitor.                              |  |  |

## MAXIMUM RATINGS (Note 1)

| Rating                                                    |                                 | Symbol                                                                     | Value                            | Unit |

|-----------------------------------------------------------|---------------------------------|----------------------------------------------------------------------------|----------------------------------|------|

| Drive Power Supply Pin to PGND                            | Pin Voltage                     | V <sub>DD</sub> - V <sub>GND</sub>                                         | -0.3 to 16                       | V    |

| Input Power Supply Pin to PGND                            | Pin Voltage                     | V <sub>IN</sub> - V <sub>GND</sub>                                         | -0.3 to 100                      | V    |

| SW Pin to PGND Pin Voltage                                | DC<br>Repetitive pulse (<100ns) | V <sub>SW</sub> - V <sub>GND</sub>                                         | -1 to 100<br>-18 to 100          | V    |

| PH Pin to PGND Pin Voltage  DC  Repetitive pulse (<100ns) |                                 | V <sub>PH</sub> - V <sub>GND</sub>                                         | -1 to 100<br>-18 to 100          | V    |

| LO Pin to VSS Pin Voltage                                 |                                 | V <sub>LO</sub> - V <sub>GND</sub>                                         | $-0.3$ to $V_{DD} + 0.3$         | V    |

| HO Pin to VSS Pin Voltage                                 |                                 | V <sub>HO</sub> - V <sub>GND</sub>                                         | $V_{PH} - 0.3$ to $V_{HB} + 0.3$ | V    |

| PWM Input LI and HI Pin to VSS Pin Voltage                |                                 | V <sub>LI</sub> - V <sub>GND</sub> ,<br>V <sub>HI</sub> - V <sub>GND</sub> | -0.3 to $V_{DD}$ + 0.3           | V    |

| Operating and Storage Temperatu                           | ure Range                       | $T_{J,}T_{STG}$                                                            | -65 to 150                       | V    |

| HB Pin to PH Pin Voltage                                  |                                 | V <sub>HB</sub> - V <sub>PH</sub>                                          | -0.3 to 16                       | V    |

| HB Pin to PGND Pin Voltage                                |                                 | V <sub>HB</sub> - V <sub>GND</sub>                                         | -0.3 to 118                      | V    |

| Lead Temperature Soldering<br>Reflow (SMD Styles Only)    |                                 | T <sub>SLD</sub>                                                           | 260                              | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

#### THERMAL CHARACTERISTICS

| Rating                                       | Symbol          | Value | Unit |

|----------------------------------------------|-----------------|-------|------|

| Thermal Characteristics                      |                 |       | °C/W |

| Thermal Resistance, Junction-to-Air (Note 2) | $R_{\theta JA}$ | 10    |      |

| Thermal Reference, Junction-to-case (Note 2) | $R_{\psiJL}$    | 2.24  |      |

R<sub>eJA</sub> is determined with the device mounted on a 1 In<sup>2</sup> pad 2 OZ copper pad on a 1.5x1.5 In. board of FR-4 material. R<sub>eJC</sub> is guaranteed by design while R<sub>eCA</sub> is determined by the user's board design and operating conditions.

## **RECOMMENDED OPERATING RANGES**

| Rating                                                                   |                 | Min | Max | Unit |

|--------------------------------------------------------------------------|-----------------|-----|-----|------|

| Input Power Voltage                                                      | VIN             | 20  | 75  | V    |

| Driver Supply Voltage DC Level                                           | $V_{DD}$        | 8   | 14  | V    |

| Switching Frequency                                                      | F <sub>SW</sub> | 20  | 410 | KHz  |

| Input PWM Signal Logic High Level (3.3V/TTL compatible input thresholds) | LI, HI          | 3   | 11  | V    |

| Operating Temperature                                                    | $T_J$           | -40 | 125 | °C   |

## **ELECTRICAL CHARACTERISTICS**

Typical value is under VIN=48 V, VDD=12 V and  $T_A=T_J=+25^{\circ}C$  unless otherwise noted.

$\label{eq:min.and} \mbox{Min. and Max. values are under VIN=48 V, VCC=PVCC=12 V$\pm$10\% and $T_J=T_A=-40^{\circ}$C to $\pm$125^{\circ}$C unless otherwise noted.}$

| Parameter                          | Test Conditions                                                  | Symbol            | Min | Тур  | Max  | Unit |

|------------------------------------|------------------------------------------------------------------|-------------------|-----|------|------|------|

| Basic Operation                    | ·                                                                | - 1               |     |      | •    |      |

| V <sub>DD</sub> Quiescent Current  | V <sub>HI</sub> =0V; V <sub>LI</sub> =0V                         | I <sub>DD</sub>   | -   | 0.17 | 0.3  | mA   |

| V <sub>DD</sub> operating Current  | Fsw = 97.5kHz                                                    | I <sub>DDO</sub>  | =   | 6.8  | -    | mA   |

| HB Quiescent current               | V <sub>HI</sub> =0V; V <sub>LI</sub> =0V                         | I <sub>HB</sub>   | =   | 0.1  | 0.2  | mA   |

| V <sub>DD</sub> UVLO Threshold     | V <sub>DD</sub> Rising                                           | $V_{DDR}$         | 6.8 | 7.6  | 8.4  | V    |

| V <sub>DD</sub> UVLO Hysteresis    |                                                                  | $V_{DDH}$         | =   | 0.6  | -    | V    |

| HB UVLO Threshold                  | HB Rising                                                        | $V_{HBR}$         | 6.0 | 7.1  | 8.1  | V    |

| HB UVLO Hysteresis                 |                                                                  | $V_{HBH}$         | -   | 0.4  | -    | V    |

| PWM Input                          | ·                                                                |                   |     |      | •    | •    |

| High Level Input Voltage Threshold |                                                                  | V <sub>IH</sub>   | 1.8 | 2.2  | 2.5  | V    |

| Low Level Input Voltage Threshold  |                                                                  | V <sub>IL</sub>   | 1.3 | 1.7  | 2.0  | V    |

| Input Logic Voltage Hysteresis     |                                                                  | V <sub>IHYS</sub> | -   | 0.5  | -    | V    |

| Input Pull-down Resistance         |                                                                  | R <sub>IN</sub>   | -   | 100  | -    | kΩ   |

| Bootstrap Diode                    |                                                                  |                   |     |      |      |      |

| Forward Voltage @ Low Current      | I <sub>VDD</sub> -HB = 100uA                                     | $V_{FL}$          | =   | 0.55 | 0.8  | V    |

| Forward Voltage @ High Current     | $I_{VDD^-HB} = 100mA$                                            | $V_{FH}$          | -   | 0.8  | 1    | V    |

| Dynamic Resistance                 | $I_{VDD^-HB} = 100mA$                                            | R <sub>D</sub>    | -   | 0.7  | 1.7  | Ω    |

| Diode Turn-on or Turn-off Time     | I <sub>F</sub> =20 mA, I <sub>REV</sub> =0.5 A                   | t <sub>BS</sub>   | =   | 20   | -    | ns   |

| Low Side Driver, LO                |                                                                  |                   |     |      |      |      |

| Low Level Output Voltage           | I <sub>LO</sub> = 100mA                                          | V <sub>OLL</sub>  | -   | 0.1  | 0.25 | V    |

| High Level Output Voltage          | $I_{LO}$ = -100mA, $V_{OHL}$ = $V_{DD}$ - $V_{LO}$               | V <sub>OHL</sub>  | -   | 0.16 | 0.3  | V    |

| Peak Pull-up Current (Note 3)      | V <sub>LO</sub> = 0V                                             | I <sub>OHL</sub>  | -   | 3    | -    | Α    |

| Peak Pull-down Current (Note 3)    | V <sub>LO</sub> = 12V                                            | I <sub>OLL</sub>  | -   | 4    | -    | Α    |

| LO Rise Time                       | 10% to 90%                                                       | t <sub>R_LO</sub> | -   | 16.9 | -    | ns   |

| LO Fall Time                       | 90% to 10%                                                       | t <sub>F_LO</sub> | =   | 15.8 | -    | ns   |

| LI=Low Propagation Delay           | $V_{LI}$ falling at 1.6V to $V_{LO}$ falling at 3.0V             | t <sub>LPHL</sub> | =   | 36   | -    | ns   |

| LI=High Propagation Delay          | V <sub>LI</sub> rising at 2.2V to V <sub>LO</sub> rising at 3.0V | t <sub>LPLH</sub> | -   | 35   | -    | ns   |

## **ELECTRICAL CHARACTERISTICS** (CONTINUED)

Typical value is under VIN=48 V, VDD=12 V and  $T_A=T_J=+25^{\circ}C$  unless otherwise noted.

Min. and Max. values are under VIN=48 V, VCC=PVCC=12 V $\pm$ 10% and T $_{J}$ =T $_{A}$ =-40°C to +125°C unless otherwise noted.

| Parameter                                 | Test Conditions                                                                | Symbol            | Min | Тур  | Max  | Unit |

|-------------------------------------------|--------------------------------------------------------------------------------|-------------------|-----|------|------|------|

| High Side Driver, HO                      |                                                                                | •                 |     |      |      | T.   |

| Low Level Output Voltage                  | I <sub>HO</sub> = 100mA                                                        | $V_{OLH}$         | -   | 0.1  | 0.25 | V    |

| High Level Output Voltage                 | I <sub>HO</sub> = -100mA, V <sub>OHH</sub> = V <sub>HB</sub> - V <sub>HO</sub> | V <sub>OHH</sub>  | -   | 0.16 | 0.3  | V    |

| Peak Pull-up Current (Note 3)             | V <sub>HO</sub> = 0V                                                           | I <sub>OHH</sub>  | -   | 3    | -    | Α    |

| Peak Pull-down Current (Note 3)           | V <sub>HO</sub> = 12V                                                          | I <sub>OLH</sub>  | -   | 4    | -    | Α    |

| HO Rise Time                              | 10% to 90%                                                                     | t <sub>R_HO</sub> | -   | 23.4 | -    | ns   |

| HO Fall Time                              | 90% to 10%                                                                     | t <sub>F_HO</sub> | -   | 17.7 | -    | ns   |

| HI=Low Propagation Delay                  | V <sub>HI</sub> falling at 1.6V to V <sub>HO</sub> falling at 3.0V             | t <sub>HPHL</sub> | -   | 39   | -    | ns   |

| HI=High Propagation Delay                 | V <sub>HI</sub> rising at 2.2V to V <sub>HO</sub> rising at 3.0V               | t <sub>HPLH</sub> | -   | 37   | -    | ns   |

| Delay Matching                            |                                                                                |                   |     |      |      |      |

| HO Turn-OFF to LO Turn-ON to              |                                                                                | T <sub>MON</sub>  | -   | 3.0  | 10   | ns   |

| LO Turn-OFF to HO Turn-ON                 |                                                                                | T <sub>MOFF</sub> | -   | 2.4  | 10   | ns   |

| Minimum Pulse Width                       |                                                                                | <u> </u>          |     | 1    | I    | 1    |

| Minimum Pulse Width for HI and LI (Note 3 |                                                                                | t <sub>PW</sub>   | -   |      | 50   | ns   |

<sup>3.</sup> These parameters are guaranteed by design.

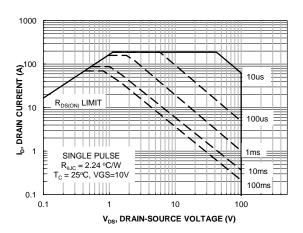

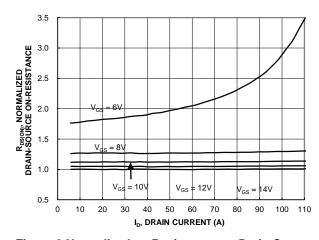

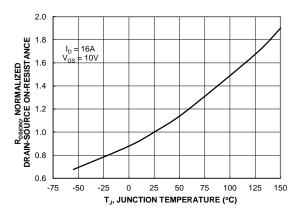

#### **TYPICAL CHARACTERISTICS**

Figure 7 Forward Bias Safe Operating Area

Figure 8 Normalized on Resistance vs. Drain Current and Gate Voltage

Figure 9 Normalized on Resistance vs. Temperature

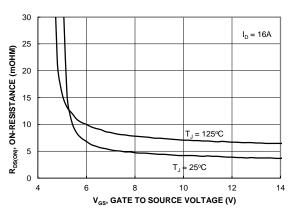

Figure 10 On Resistance vs. Gate to Source Voltage

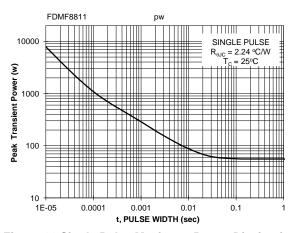

Figure 11 Single Pulse Maximum Power Dissipation

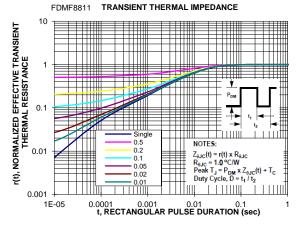

**Figure 12 Junction to Ambient Transient Thermal**

## **TYPICAL CHARACTERISTICS**

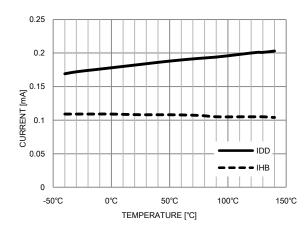

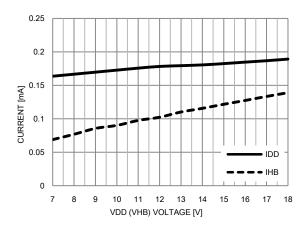

Figure 13 Driver Quiescent Current vs. Temperature

Figure 14 Driver Quiescent Current vs.  $V_{DD}$  ( $V_{HB}$ )

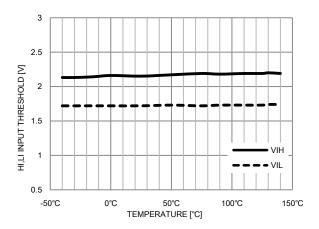

Figure 15 Input Threshold vs. Temperature

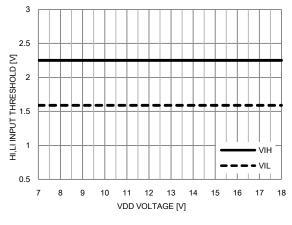

Figure 16 Input Threshold vs. V<sub>DD</sub>

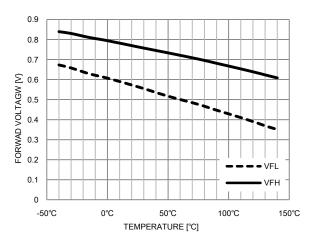

Figure 17 Boost strop Diode V<sub>F</sub> vs. Temperature

## **Switching Time Definitions**

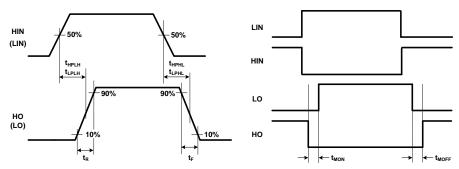

Figure 18 shows the switching time waveforms definitions of the turn on and off propagation delay times.

Figure 18. Timing Diagrams

## **Input to Output Definitions**

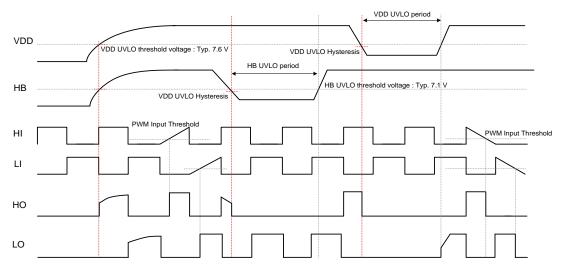

Figure 19 shows an input to output timing diagram for overall operation.

Figure 19. Overall Operation Timing Diagram

#### **APPLICATIONS INFORMATION**

The FDMF8811 co-packages one driver IC with integrated bootstrap diode, one low side 100V power MOSFET and one high side 100V power MOSFET in a thermally enhanced, compact 6.0 mm x 7.5 mm PQFN package. To perform the half bridge power module function, two 3.3V/TTL compatible PWM input signals are connected to the FDMF8811's LI and HI pins. The inside driver IC will converter the two input PWM signals into driver signals LO and HO for both low side and high side power MOSFET. A bootstrap capacitor recommended value being 100nF is required to be connected between HB and PH pin to provide floated driver signal for high side power MOSFET.

## **Driver Power Supply**

Driver power supply quality is very important in DC-DC power applications. First, voltage level of the driver power supply determines pull up/pull down strength of the driver's output signals, switching speed and power conversion efficiency. The higher the DC level of driver power supply is, the higher the pull up and pull down strength is. Second, the DC level of drive power supply determines the operation mode of power MOSFET conducting large current. If the level is low, the power MOSFET safe operation area (SOA) as specified in the power device characteristics will become smaller and its current conduction ability is degraded. If the level is too low, the power MOSFET might even work in saturation region in some cases to cause device damage. Third, the DC level of driver power supply affects the propagation delay inside the drivers and the drain to source voltage stress on the power MOSFET. In high performance power applications, the above factors need to be well controlled by designing a high quality driver power supply circuit to ensure consistent switching performance and best power conversion efficiency. As the FDMF8811 is optimized to operate in VDD=10V, our recommended driver power supply is 10V DC level with less than 100mV peak to peak ripple.

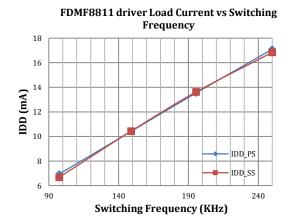

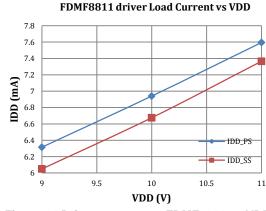

When customer consider upgrading their nowadays components with FDMF8811, they need to be aware that the load current of the driver power supply might be significantly decreased in comparison with their nowadays solutions with discrete MOSFETs or other companies' components. The reason is that applies the most advanced device technology FDMF8811, so the gate charging current is significantly less and the customer is expected to see around 6.8mA load current when driving one FDMF8811 with 10V VDD and 97.5KHz switching frequency.

We notice that some Flyback based VDD power supply circuit might present oscillation when load current becomes less than 10mA, so recommends customer to first evaluate and improve their nowadays driver power supply circuit, then power up the whole DC-DC system with the FDMF8811s.

For the convenience of customer to design their VDD power supply system, Figure 20 and Figure 21 provides typical VDD power supply load current of the FDMF8811 and its relationship with VDD level and switching frequency.

Figure 20 Driver current per FDMF8811 vs switching frequency

Figure 21 Driver current per FDMF8811 vs VDD

#### Start Up / Shut Down Sequence

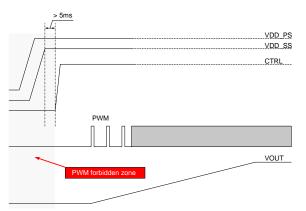

When powering up a DC-DC conversion system or recovering the system from fault conditions, a correct start up timing sequence is highly recommended to avoid overstress or even damage of the components in the system. It is highly recommended to configure the power system to have more than 5 milliseconds time margin between the event that the driver power supplies are turned on and the event the system sends out CTRL signal to activate the controller PWM, so that PWM signals are ensured not presenting in the PWM forbidden zone illustrated in Figure 22. "VDD\_PS" in Figure 22

refers to VDD power supply at primary side and "VDD\_SS" refers to VDD power supply at secondary side.

Figure 22 VDD power supply timing sequence during start up

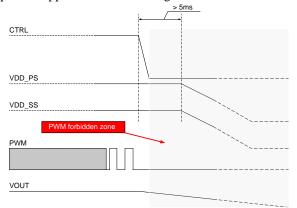

A correct timing sequence is also required when powering down a DC-DC conversion system to avoid overstress or even damage of the components in the system. It is highly recommended to configure the power system to have more than 5 milliseconds time margin between the event that the controller pulls down PWM signals and the event the driver power supplies are turn off. The PWM forbidden region illustrated in Figure 23 suggests no PWM signal 5 milliseconds before VDD power supplies starts to lose regulation.

Figure 23 VDD power supply timing sequence during power down

## **PCB Layout Guideline**

There are several loops with the high frequency pulsing current, including the input voltage loop and two gate driver loops. It is critical to keep the loop impedance as low as possible. All of the high current paths, such as VIN, SW and PGND, should be short and wide for low parasitic inductance and resistance. This helps achieve a more stable and evenly distributed current flow, along with enhanced heat radiation and system performance.

Input ceramic bypass capacitors must be close to the VIN and PGND pins. This reduces the high-current power loop inductance and the input current ripple induced by the power MOSFET switching operation.

The SW copper trace serves two purposes. In addition to being the high-frequency current path from the FDMF8811 package to the output inductor, it serves as a heat sink for the low-side MOSFET in the FDMF8811 package. The trace should be short and wide enough to present a low-impedance path for the high-frequency, high-current flow between the FDMF8811 and inductor. The short and wide trace minimizes electrical losses as well as the FDMF8811 temperature rises.

Note that the SW node is a high-voltage and high-frequency switching node with high noise potential. Care should be taken to minimize coupling to adjacent traces. Since this copper trace acts as a heat sink for the low-side MOSFET, balance using the largest area possible to improve FDMF8811 cooling while maintaining acceptable noise emission.

An output inductor should be located close to the FDMF8811 to minimize the power loss due to the SW copper trace. Care should also be taken so the inductor dissipation does not heat the FDMF8811.

PowerTrench® MOSFETs are used in the output stage and are effective at minimizing ringing due to fast switching. In most cases, no R&C snubber on SW node is required. If a snubber is used, it should be placed close to the SW and PGND pins.

The board layout should include a placeholder for small-value series boot resistor in series to the BOOT capacitor. The boot-loop size, including series RBOOT and CBOOT, should be as small as possible.

The boot resistor may be required when there is large ringing at SW pin, and it is effective to control the high-side MOSFET turn-on slew rate and SW voltage overshoot. RBOOT can improve noise operating margin if there is large switching noise due to ground bounce or high positive and negative SW ringing. Inserting a boot resistance lowers the FDMF8811 module efficiency. Efficiency versus switching noise trade-offs must be considered.

The VIN and PGND pins handle large current transients with frequency components greater than 100MHz. If possible, these pins should be connected directly to the VIN and board GND planes. The use of thermal relief traces in series with these pins is not recommended since this adds extra parasitic inductance to the power path. This added inductance in series with either the VIN or PGND pin degrades system noise immunity by increasing positive and negative SW ringing.

PGND pad and pins should be connected to the GND copper plane with multiple vias for stable grounding. Poor grounding can create a noise transient offset

voltage level between PGND and VSS. This could lead to faulty operation of gate driver and MOSFETs.

Ringing at the BT pin is most effectively controlled by close placement of the boot capacitor. Do not add any additional capacitors between BT to PGND. This may lead to excess current flow through the BT diode, causing high power dissipation.

Put multiple vias on the VIN and VOUT copper areas to interconnect top, inner, and bottom layers to evenly distribute current flow and heat conduction. Do not put too many vias on the SW copper to avoid extra parasitic inductance and noise on the switching waveform. As long as efficiency and thermal performance are acceptable, place only one SW node copper on the top layer and put no vias on the SW copper to minimize switch node parasitic noise. Vias should be relatively large and of reasonably low inductance. Critical highfrequency components, such as RBOOT, CBOOT, R&C snubber, and bypass capacitors should be located as close to the respective FDMF8811 module pins as possible on the top layer of the PCB. If this is not feasible, they can be placed on board bottom side and their pins can be connected from bottom to top through a network of low-inductance vias..

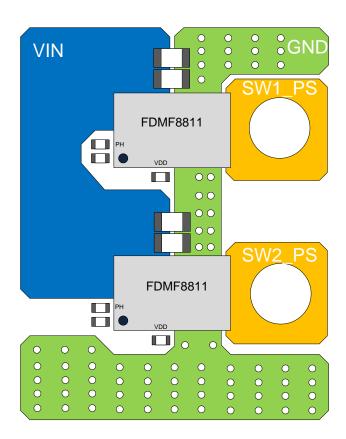

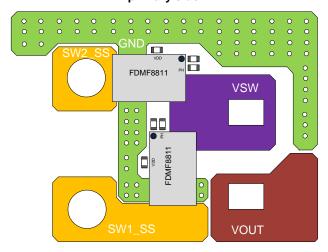

Figure 24 and Figure 25 show example top layer layout of the FDMF8811s Full Bridge application on primary side and secondary side.

Figure 24 Example layout of FDMF8811 Full Bridge primary side

Figure 25 Example layout of FDMF8811 Full Bridge secondary

#### **ORDERING INFORMATION**

| Device   | Output Configuration   | Marking  | Package | Shipping †  |

|----------|------------------------|----------|---------|-------------|

| FDMF8811 | High-Side and Low-Side | FDMF8811 | PQFN    | Tape & Reel |

## **PACKAGE DIMENSIONS**

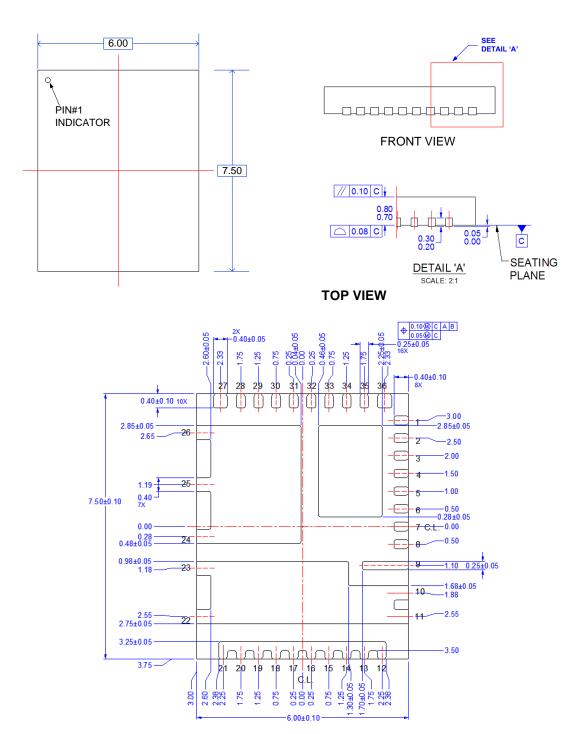

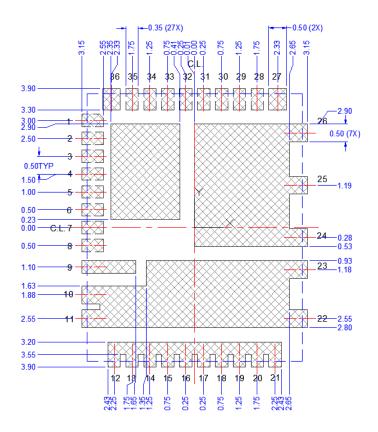

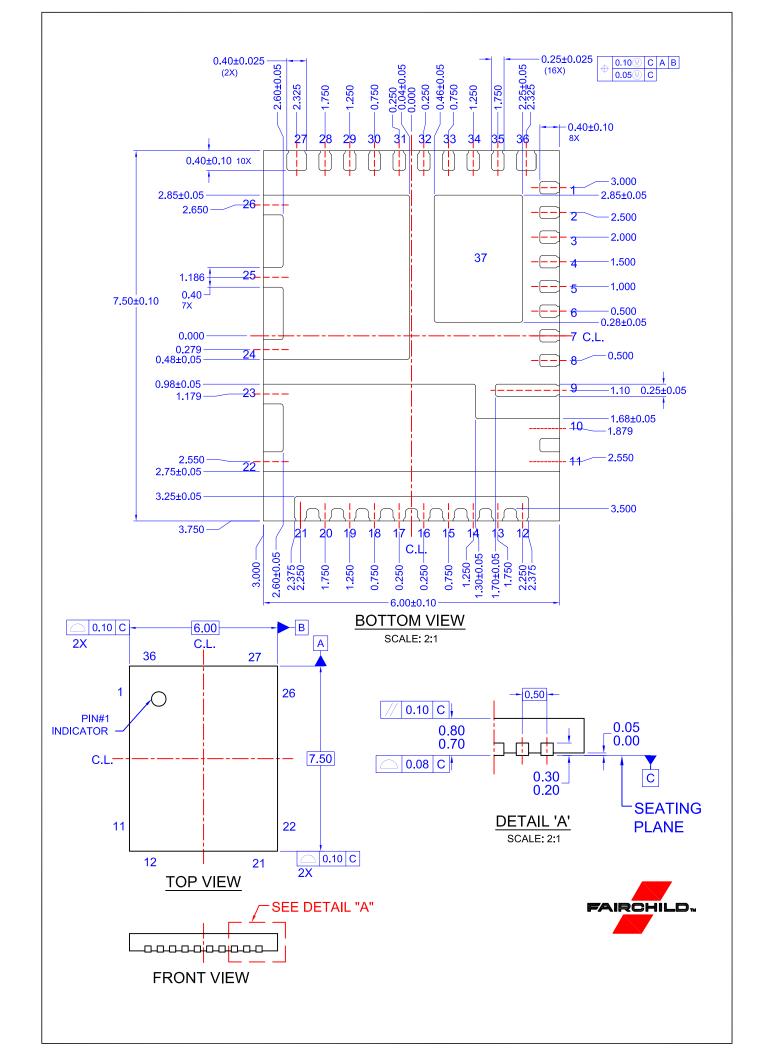

Figure 26. Clip Bond PQFN 6.0mm x 7.5mm Package

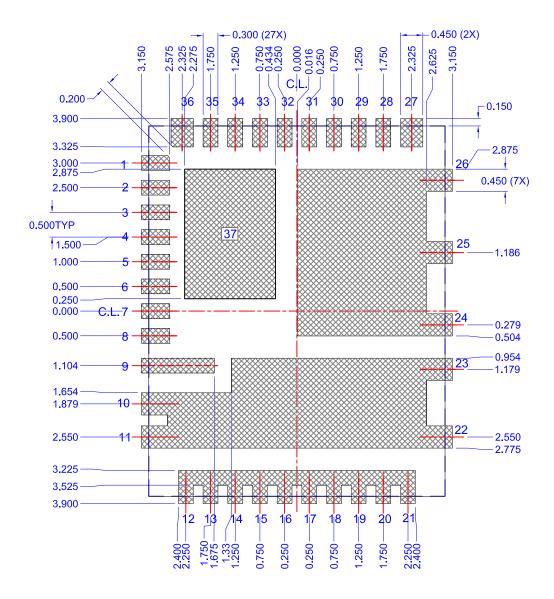

#### **Land Pattern Recommendation**

Note: Line in red is the package size outline of 6.0 x 7.5 mm

Figure 27. Clip Bond PQFN 6.0mm x 7.5mm Package Land Pattern Recommendation

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by

ON Semiconductor: "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or intended for implantation in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

## PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada.

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center Phone: 81-3-5817-1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

## LAND PATTERN RECOMMENDATION

SCALE 2:1

#### NOTES: UNLESS OTHERWISE SPECIFIED

- A) DOES NOT FULLY CONFORM TO JEDEC MO-220, ISSUE K.01, DATED AUG 2011.

- B) ALL DIMENSIONS ARE IN MILLIMETERS.

- C) DIMENSIONS DO NOT INCLUDE BURRS OR MOLD FLASH. MOLD FLASH OR BURRS DOES NOT EXCEED 0.10MM.

- D) DIMENSIONING AND TOLERANCING PER ASME Y14.5M-2009.

- E) DRAWING FILE NAME: MKT-PQFN36BREV3

ON Semiconductor and in are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdt/Patent-Marking.pdf">www.onsemi.com/site/pdt/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and exp

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative