As AI processors move deeper into multi-kilowatt territory, power delivery is no longer a supporting function—it’s becoming a primary system constraint. At APEC 2026, Empower Semiconductor is using that shift as the backdrop for showcasing its latest work in vertical power delivery (VPD), including updates to its Crescendo platform and a preview of next-generation current density advancements.

The company will exhibit at Booth #712, focusing on how power architectures are evolving to support increasingly demanding AI and high-performance computing (HPC) workloads.

Power Delivery Becomes the Bottleneck

For years, performance scaling in compute platforms was driven by advances in silicon. That dynamic is changing. As AI accelerators push past the kilowatt threshold, delivering clean, stable power at high current levels is becoming one of the hardest problems in system design.

Traditional board-level power delivery architectures struggle to keep up. Long power paths introduce losses, parasitics, and voltage droop—issues that are amplified at the current levels required by modern AI processors.

Empower’s approach with vertical power delivery shifts regulation closer to the load, reducing path length and improving both efficiency and transient response.

Moving Power Into the Package

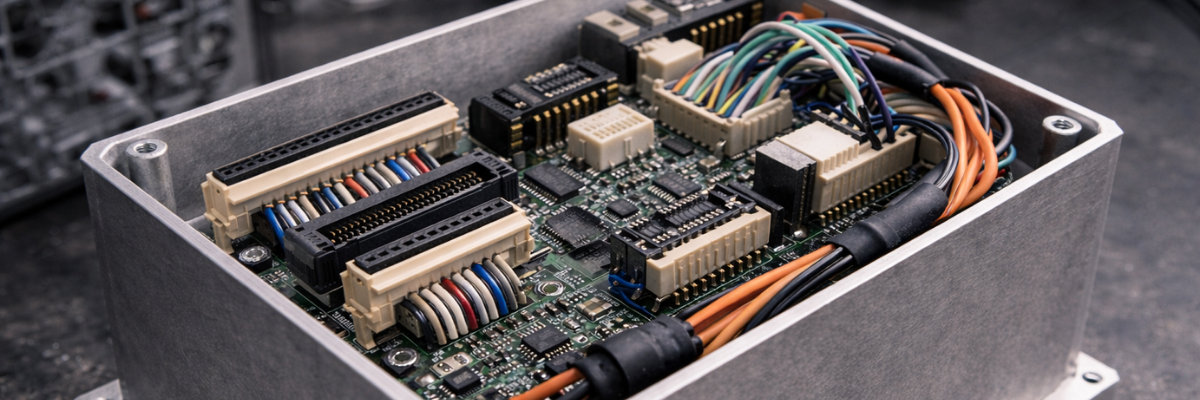

The Crescendo VPD platform is designed to move beyond conventional PCB-based voltage regulation by integrating power delivery more tightly with the processor.

Instead of relying solely on board-level regulators, VPD architectures bring power conversion closer to—or even inside—the package. This reduces distribution losses and allows for faster response to dynamic load changes, which are common in AI workloads.

At APEC, Empower is expected to demonstrate how this approach supports higher bandwidth power delivery while maintaining tight voltage regulation under rapidly changing conditions.

Pushing Current Density Higher

One of the key metrics for next-generation power systems is current density—how much current can be delivered per unit area.

Empower’s latest developments aim to push toward the 5A/mm² range, a level increasingly required by next-generation AI platforms. Achieving this requires not just better regulators, but a rethinking of how power is distributed and decoupled across the system.

The company’s roadmap includes enhancements to its Crescendo platform, along with new technologies designed to further increase current density without sacrificing efficiency or thermal performance.

The Role of Integrated Capacitance

Power integrity is another critical challenge at these power levels. Fast transient loads can cause voltage fluctuations that impact processor stability and performance.

Empower addresses this through its silicon capacitor technology, which is designed to provide high-performance decoupling in a compact footprint. By integrating capacitance closer to the load, the system can respond more effectively to rapid current demands.

This becomes especially important in AI and HPC environments, where workloads can shift quickly and unpredictably.

Industry Momentum Behind VPD

Vertical power delivery is gaining attention as a long-term solution for scaling compute platforms. While large semiconductor companies are expected to dominate near-term voltage regulator deployments, emerging architectures like VPD are creating opportunities for new entrants.

Empower’s positioning reflects this transition. By focusing on system-level power challenges—rather than discrete components—the company is aligning with the broader shift toward co-optimized hardware design in AI systems.

APEC Sessions to Watch

In addition to its booth demonstrations, Empower will contribute to two industry sessions at APEC 2026 focused on the evolving challenges of powering AI processors:

-

Vertical Power Delivery Integration: Benefits and Trade-offs of Moving Beyond PCB Backside to In-package Solutions

-

Powering the Kilowatt-Class AI Processors Era: A State-of-the-Industry Review of Scalable Power Delivery Solutions for Compute Platforms

Both sessions are expected to explore the trade-offs between traditional and emerging power architectures, including integration complexity, thermal considerations, and scalability.

A Shift in System Design Priorities

The broader takeaway is that power delivery is moving into the critical path of system performance. As AI processors continue to scale, the ability to deliver high current with minimal loss and tight regulation will directly influence achievable compute performance.

Technologies like VPD suggest a shift away from treating power as a board-level problem and toward integrating it as a core part of the compute architecture itself.