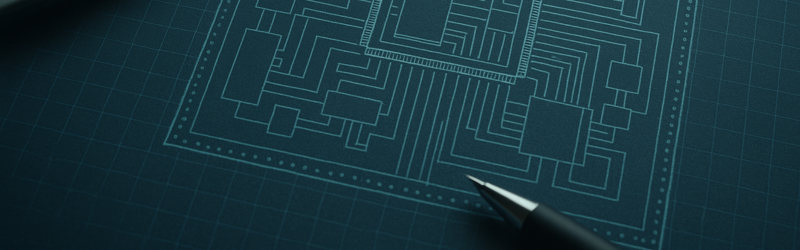

Designing an AI chip doesn’t begin in a cleanroom. It starts long before tape-out, when engineers are mapping workloads, testing architectural options, and weighing trade-offs on paper and in simulation. That early phase, the pre-silicon planning, is where performance, power, and schedule risks are discovered and managed.

Why the Early Stage Matters

AI chips have become central to modern computing, powering cloud infrastructure, autonomous vehicles, and edge devices. With that role comes higher stakes. Misjudgments in architecture or memory planning can turn into redesigns that cost months of time and millions of dollars [1][2].

Workload First

The starting point is the workload. A chip designed for large-scale training requires different choices than one focused on low-power inferencing at the edge. Training emphasizes throughput and memory bandwidth. Inferencing often prioritizes latency and efficiency.

Studies of deep learning accelerators confirm that memory bandwidth, not raw compute, is now the most common limiter in AI performance [3][4]. That insight changes how architects plan: instead of maximizing flops alone, they model how data moves across caches, DRAM, and interconnects.

Exploring Architectures Before Hardware Exists

Pre-silicon planning relies heavily on modeling and simulation. Virtual prototypes allow teams to explore options—doubling cache, widening an interconnect, or shifting clock speeds—and measure the impact on power, die size, and throughput.

The IEEE Heterogeneous Integration Roadmap notes that system-level modeling can expose power and performance bottlenecks early, reducing the risk of expensive re-spins [5]. Arm has shown that virtual prototyping not only helps hardware teams but also gives software engineers a platform to begin development months before silicon arrives [7].

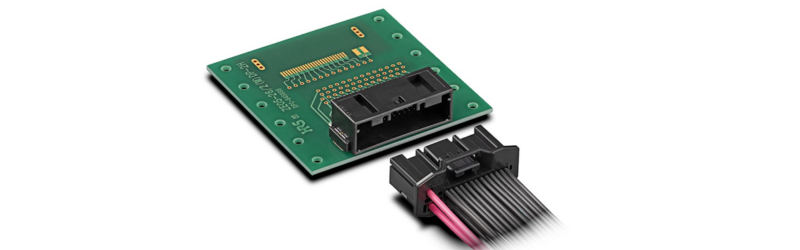

Integrating IP and Security Early

Most AI chips combine third-party IP such as CPU cores and memory controllers with custom accelerators. Each block introduces its own performance limits and security risks. The IEEE Heterogeneous Integration Roadmap highlights that supply chain vulnerabilities in IP are a significant security concern if not addressed during pre-silicon planning [6]. Early validation ensures integration challenges are surfaced before detailed implementation begins.

Validating More Than Just Speed

Performance is not the only metric. Planning also tests manufacturability, reliability, and test coverage. Virtual prototypes and architecture exploration tools like Synopsys Platform Architect are used to verify that designs can be built, validated, and supported on the chosen process node [9][10].

Why Planning Defines the Chip

By the time a mask set is written, most important decisions are locked in. Pre-silicon planning is where compute fabrics are sized, memory budgets are set, and integration risks are solved. Once those choices are captured in silicon, they are difficult to undo.

The blueprint, in other words, is harder than the silicon. Get it right, and the rest is execution. Get it wrong, and no amount of late-stage optimization will rescue the design.

The Road Ahead

With AI workloads growing in size and diversity, pre-silicon planning is expanding to include more accurate workload modeling, closer collaboration between hardware and software engineers, and cross-domain simulation. The goal is straightforward: reduce late-stage surprises and shorten the path from whiteboard to working chip.

References

-

-

Synopsys. Building an AI Chip: Pre-Silicon Planning.

https://www.synopsys.com/ai/ai-chip-development/building-an-ai-chip-pre-silicon-planning.html -

TechOnline. Building an AI Chip: Pre-Silicon Planning.

https://www.techonline.com/tech-papers/building-an-ai-chip-pre-silicon-planning/ -

ACM TACO. An Application-Oblivious Memory Scheduling System for DNN Accelerators, Dec 2022.

https://dl.acm.org/doi/10.1145/3535355 -

PVLDB. Overcoming the Hurdles of GPU Memory Capacity to Train Massive Models on a Single Server (Harmony).

https://vldb.org/pvldb/vol15/p2747-li.pdf -

IEEE Electronics Packaging Society. Heterogeneous Integration Roadmap 2021, Chapter 14: Modeling and Simulation.

https://eps.ieee.org/images/files/HIR_2021/ch14_sim.pdf -

IEEE Electronics Packaging Society. Heterogeneous Integration Roadmap 2021, Chapter 19: Cyber Security.

https://eps.ieee.org/images/files/HIR_2021/ch19_security1.pdf -

Arm. The Power of Virtual Prototyping: From SoC Design to Software Development.

https://armkeil.blob.core.windows.net/developer/Files/pdf/white-paper/virtual-prototyping-soc-design.pdf -

DVCon. Bridging the Gap Between System-Level and Chip-Implementation Verification Flows.

https://dvcon-proceedings.org/wp-content/uploads/91853.pdf -

Synopsys. Platform Architect: SoC Architecture Analysis and Optimization.

https://www.synopsys.com/verification/virtual-prototyping/platform-architect.html -

Semiconductor Engineering. Virtual Prototype.

https://semiengineering.com/knowledge_centers/eda-design/verification/virtual-prototype/

-