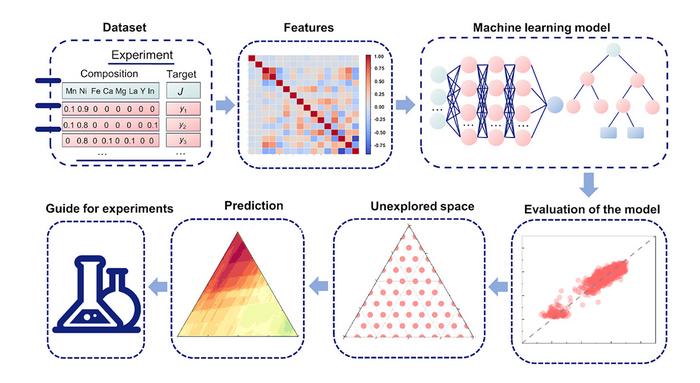

Huawei and Semiconductor Manufacturing International Co. (SMIC) patented lithography methods earlier this year to produce advanced microchips. Most assumed that the companies were working on chips using their 5-nm class fabrication process; however, it seems that Huawei is also looking to use the 3nm-class manufacturing methods. 5nm-class chips were predictable, but using quadruple patterning for 3nm-class nodes was a surprise.

5nm-class nodes shrink metal pitches to 30nm–32nm. At 3nm, metal pitches reach approximately 21nm–24nm, enabling critical dimensions of roughly 12nm for high-volume manufacturing, which even Low-NA EUV tools cannot achieve without double patterning. Yet it looks like Huawei and SMIC plan to get there.

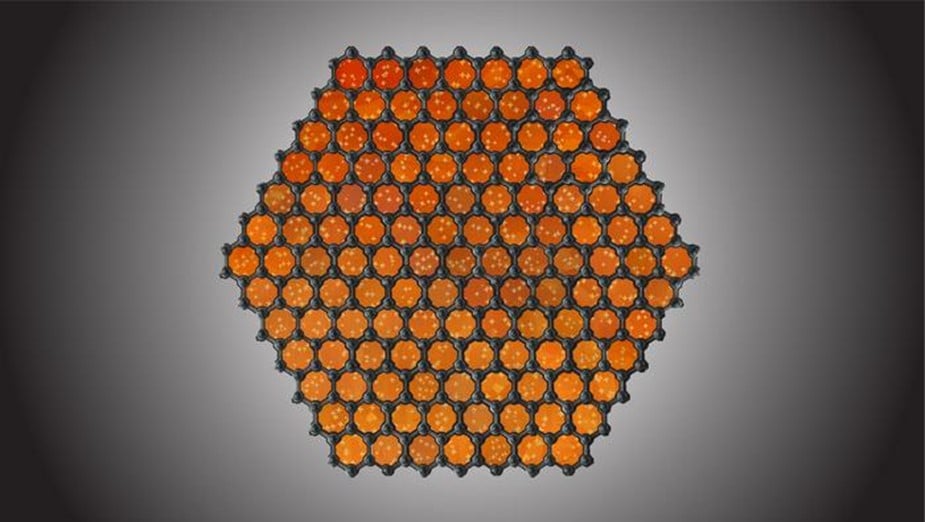

SAQP is crucial for Huawei and SMIC as they cannot access ASML’s Twinscan NXT:2100i and Twinscan NXE:3400C/3600D/3800E because of export rules imposed by the Netherlands, at the instigation of the U.S. SAQP involves repeatedly etching lines on silicon wafers that increase transistor density, reduce power consumption, and enhance performance.

SAQP’s use still presents challenges. Intel’s first-generation 10nm-class process technology based on this method failed. Yields were said to be so bad that the only 10nm Canon Lake CPU only had two CPU cores, and the integrated graphics was disabled. For SMIC, SAQP is necessary to progress in semiconductor technology, enabling the production of more sophisticated chips for consumer devices and A.I. servers.

Even at its high cost, the method is vital for China’s advancements in semiconductor technology.