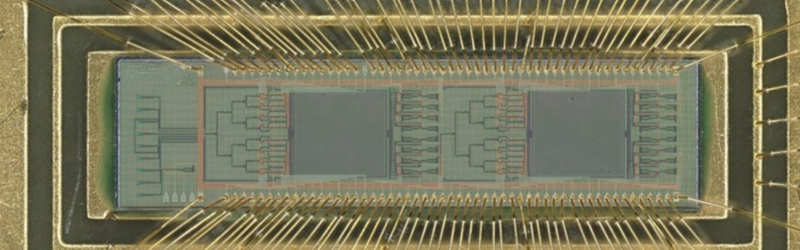

As data center workloads scale with artificial intelligence (AI) and high-performance computing (HPC), the bottleneck has shifted from compute power to data movement. Addressing this challenge, Microchip Technology has introduced its Switchtec™ Gen 6 PCIe® switches, the industry’s first built on a 3 nm process.

The new generation supports up to 160 lanes of PCIe 6.0 connectivity, doubling per-lane throughput to 64 GT/s and improving overall data flow between CPUs, GPUs, accelerators, and memory in high-density servers. The 3 nm process also enables lower power consumption—critical for scaling AI fabrics efficiently within hyperscale and cloud environments.

Architecting for AI Data Flow

Earlier PCIe generations often limited performance due to bandwidth constraints between processors and accelerators. PCIe 6.0 alleviates those constraints by adopting Flow Control Unit (FLIT) mode, a lightweight Forward Error Correction (FEC) scheme, and dynamic resource allocation. Together, these updates reduce latency and enhance reliability during the high-volume, small-packet transfers typical of AI workloads.

The Switchtec Gen 6 family expands upon Microchip’s existing interconnect solutions with configurations featuring 20 ports and 10 stacks, each capable of hot- and surprise-plug control. The devices also support:

-

Non-Transparent Bridging (NTB) for multi-host domain connectivity

-

Multicast for one-to-many data transfers

-

Advanced error containment, diagnostics, and debug functions

-

Integrated MIPS processor and bifurcation at x8 and x16

These capabilities make the switches well-suited for modern rack-level designs where GPUs, CPUs, and storage function as pooled resources rather than discrete systems.

Security and Reliability Built In

The Switchtec Gen 6 devices incorporate a hardware root of trust and secure boot framework that use post-quantum safe cryptography, aligned with the Commercial National Security Algorithm Suite (CNSA) 2.0. This hardware-based security model ensures system integrity from power-up through runtime operation—an increasingly critical factor in AI-focused data centers handling sensitive datasets.

Development Ecosystem

Microchip supports the Switchtec Gen 6 line with its ChipLink diagnostic suite, providing configuration, debugging, and performance monitoring through a graphical interface. ChipLink can connect via in-band PCIe or sideband interfaces such as UART, TWI, or EJTAG.

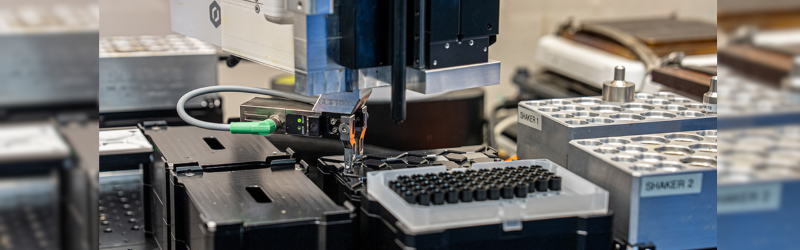

For prototyping, the PM61160-KIT Switchtec Gen 6 PCIe Switch Evaluation Kit provides multiple connectivity options and full access to configuration parameters.

Availability

Switchtec Gen 6 PCIe switches are now available for sampling to qualified customers.