Altera, now the Programmable Solutions Group (PSG) within Intel Corporation, unveiled the transceiver technology that will enable Stratix 10 FPGAs and SoCs to support data rates up to 56 Gbps. Altera is demonstrating today the FPGA industry’s first dual-mode 56-Gbps pulse-amplitude modulation with 4-levels (PAM-4) and 30-Gbps non-return-to-zero (NRZ) transceivers. The transceiver technology doubles the bandwidth available on a single transceiver channel, while providing equipment manufacturers scalability to build future systems. Stratix  10 FPGAs and SoCs are optimized to support the massive amounts of data that are being transmitted across copper backplanes and optical interconnects used in data center infrastructure and telecommunications equipment.

10 FPGAs and SoCs are optimized to support the massive amounts of data that are being transmitted across copper backplanes and optical interconnects used in data center infrastructure and telecommunications equipment.

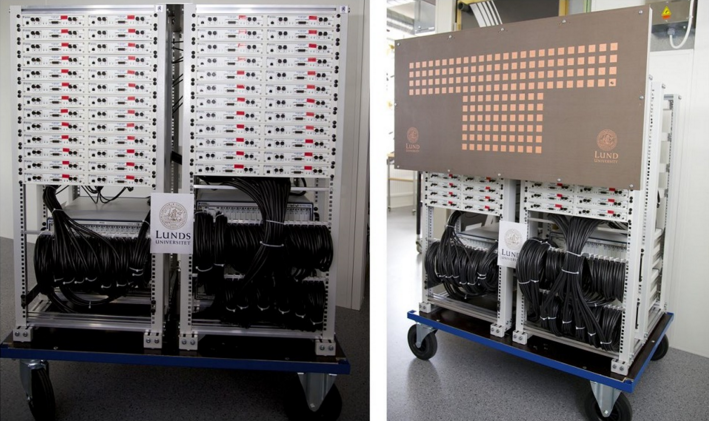

The Stratix 10 FPGA transceiver technology will support data rates ranging from 1 Gbps to 56 Gbps. Customers can use Stratix 10 FPGAs to build next-generation communications and networking infrastructure that support 50G, 100G, 200G, 400G and terabit applications. The transceiver’s dual mode capabilities provide customers a path to develop next-generation high-end systems, while also providing investment protection by supporting mainstream and legacy backplanes, copper cables, chip-to-chip and chip-to-module interconnects and interfaces. Altera has been an industry recognized leader and contributor to the 50G-56G PAM-4 standard within the IEEE 802.3 Ethernet and Optical Internetworking Forum (OIF).

“Today’s explosive growth in bandwidth requirements for data centers and network infrastructure requires that our FPGA’s power and density efficiently transmit more data, faster,” said Jordon Inkeles, director of marketing, high-end products, Programmable Solutions Group, Intel Corporation. “As systems require data rates beyond 28 Gbps, traditional NRZ modulation schemes for data transmission are struggling to keep pace. The implementation of dual-mode 56-Gbps PAM-4 and 30-Gbps NRZ transceivers into our Stratix 10 FPGAs and SoCs will enable customers to address the most demanding data throughput requirements.”

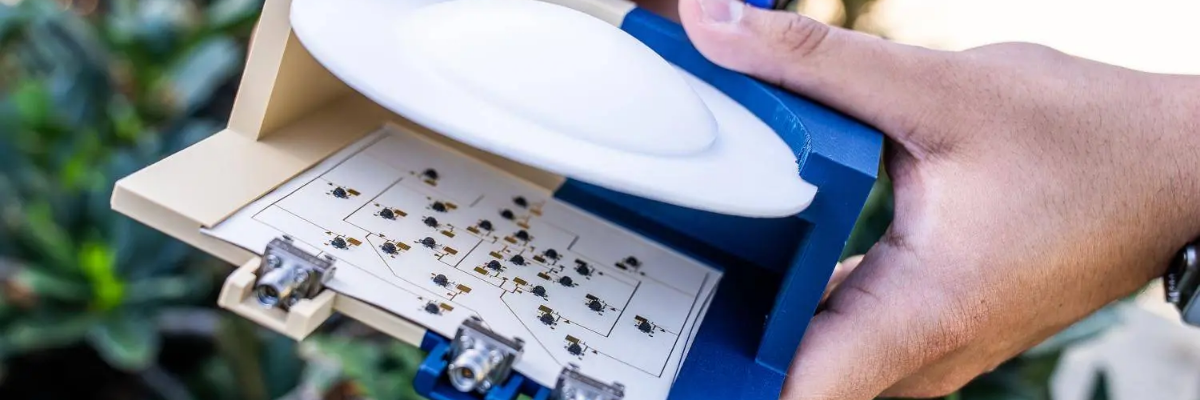

Stratix 10 FPGA transceivers are integrated using a heterogeneous system-in-package (SiP) approach. Transceiver tiles are combined with a monolithic FPGA core fabric using Intel’s Embedded Multi-die Interconnect Bridge (EMIB) technology, which allows Stratix 10 FPGAs and SoCs to rapidly address the ever-increasing system bandwidth demands across virtually every market segment. A transceiver tile approach offers greater flexibility, scalability and faster time-to-market.

Availability

Initial Stratix 10 FPGAs will start shipping in Q4 2016. Altera is demonstrating the Stratix 10 FPGA transceiver technology at OFC 2016.