It has been announced by Arm, Cadence Design Systems, and Xilinx, that the delivery of a new development platform, silicon-proven on TSMC’s 7nm FinFET process technology, for next-generation cloud-to-edge infrastructure based on the new Arm Neoverse N1 platform. The Neoverse N1 System Development Platform (SDP) is a 7nm infrastructure development platform enabling asymmetrical compute acceleration via the CCIX interconnect architecture.

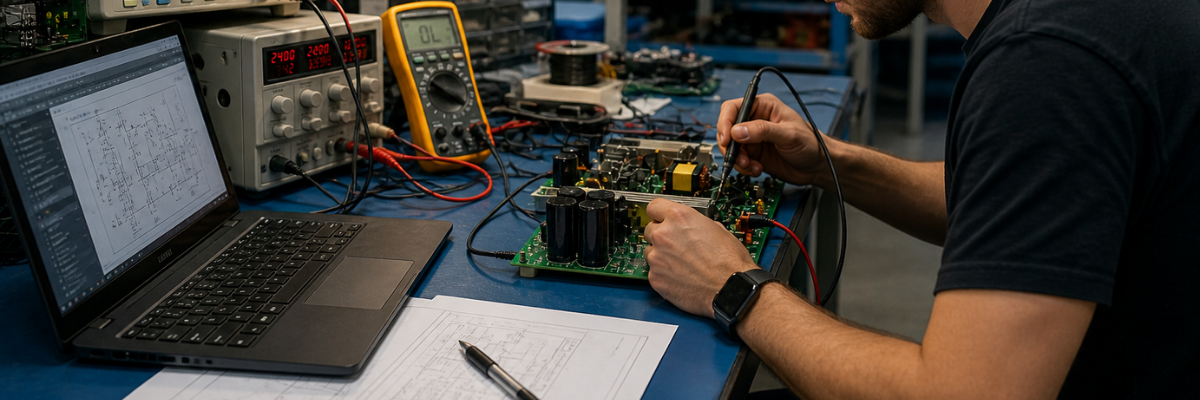

It is available to hardware and software developers for hardware prototyping, software development, system validation, and performance profiling/tuning.

The SDP includes a Neoverse N1-based SoC with an operating frequency of up to 3GHz, full-sized caches and generous amounts of memory bandwidth with the latest optimized system IP. The robustness of the SDP is ideal for development, debug, performance optimization and workload analysis on a wide range of applications including those for machine learning (ML), artificial intelligence (AI) and data analytics.

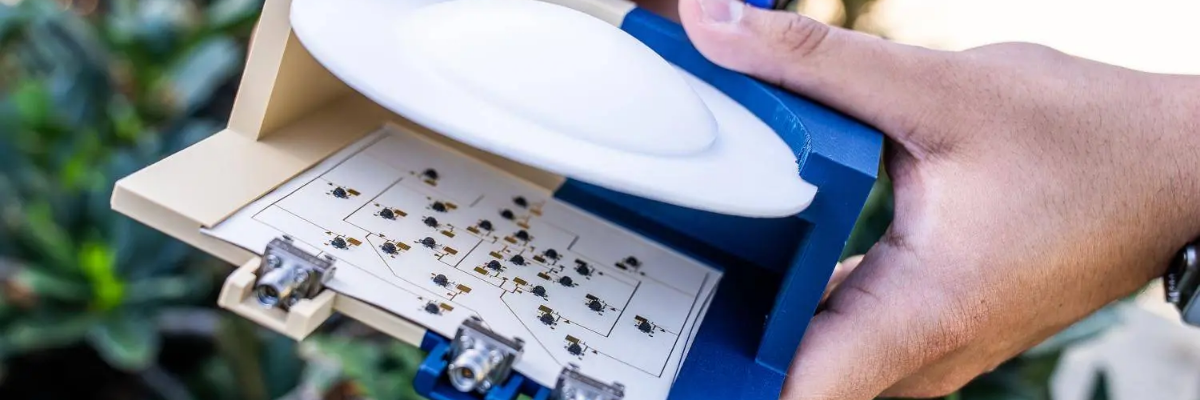

The Neoverse N1 SDP was developed jointly by Arm, Cadence and Xilinx on TSMC’s process technology, and includes Cadence IP for CCIX, PCI Express (PCIe) Gen 4 and DDR4 PHY IP. The SDP was implemented and verified using a full Cadence tool flow in TSMC’s 7nm FinFET process technology, and provides connectivity to Xilinx Virtex UltraScale+ FPGAs over the CCIX chip-to-chip coherent interconnect protocol via the Xilinx Alveo U280 CCIX accelerator card.

For customers with intense compute workloads, CCIX offers a significant accelerator usability improvement as well as improved data center performance/efficiency, lowering the barrier to entry into existing server infrastructure systems and improving the total cost of ownership (TCO) of acceleration systems.

The Neoverse N1 SDP will be available in limited quantities in Q2 2019 with wider availability in subsequent quarters. The software stack can be accessed through Linaro and GitHub open-source repositories providing developers with an out-of-the-box Linux software experience. The Xilinx Alveo U280 accelerator card, which features a high-performance FPGA with integrated high-bandwidth memory (HBM) and a CCIX interface, is available now and can be purchased directly from Xilinx.

Additionally, the full Cadence SoC implementation and verification flows, CCIX, PCIe Gen 4 and DDR4 IP, and the Neoverse N1 Rapid Adoption Kit (RAK) are available now, so customers can begin designing Neoverse N1-based SoCs on TSMC’s 7nm silicon immediately.

Drew Henry, Senior Vice President and General Manager, Infrastructure Line of Business, Arm, stated: “The new Neoverse platforms deliver the performance and efficiency required to enable the cloud-to-edge infrastructure for a world with a trillion connected devices. Our ongoing SDP collaboration with Cadence, TSMC, and Xilinx truly enables developers with the system development tools necessary to innovate and deliver optimized Neoverse-based designs.”

Dr Anirudh Devgan, President, Cadence, added: “Through our collaboration with Arm, TSMC and Xilinx, we are jointly working to advance next-generation cloud-to-edge infrastructure. By contributing our IP and EDA tools and flows to the development of the Neoverse N1 SDP, we’re enabling customers to use the full Cadence implementation and verification flows, infrastructure IP, and rapid adoption kit to develop their own devices today for machine learning, 5G, analytics and other evolving application areas that enable them to excel in their respective markets.”

Dr Cliff Hou, VP Technology Development, TSMC, continued: “This collaborative effort combines Arm, Cadence and Xilinx’s leading products, IP and tools with TSMC’s 7nm FinFET process technology and foundry services, enabling our customers to achieve faster and successful application development in areas including machine learning/AI, 5G and analytics, and creating greater value to the markets that will be fundamentally transformed by those applications.”

Gaurav Singh, Corporate Vice President, Silicon Architecture and Verification, Xilinx: “The ARM Neoverse N1 CCIX-enabled SDP with the Alveo accelerator card is a highly-performant platform designed to enable the next generation of applications to be developed. The seamless data-sharing among the heterogeneous devices demonstrates the successful integration of CCIX IP from multiple vendors and the expanding reach of CCIX technology.”