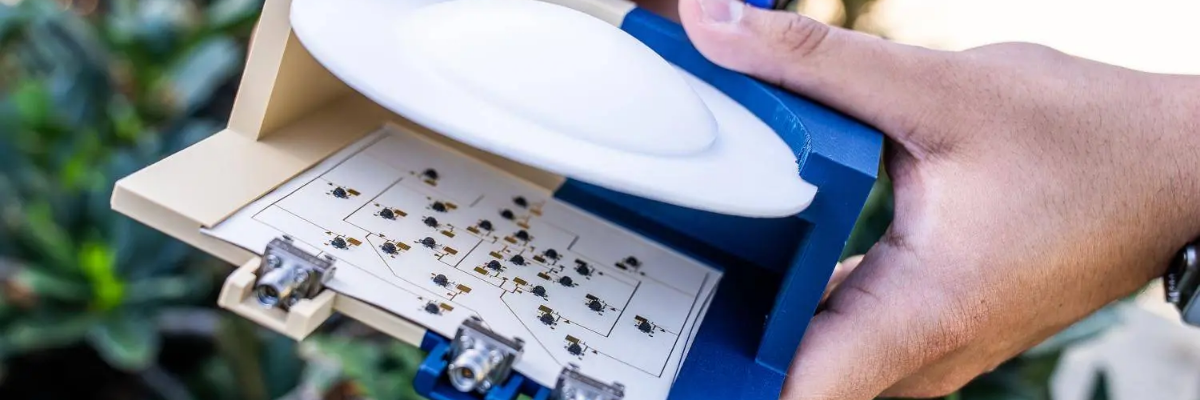

Synopsys has announced availability of design solutions to support Samsung Foundry’s 2.5D-IC Multi-Die Integration (MDI) on its 7-nanometer (nm) LPP (Low Power Plus) with extreme ultraviolet (EUV) lithography technology, known as 7LPP.

The Synopsys Fusion Design Platform and Custom Design Platform enable quicker design prototyping and analysis to help designers address the time-to-market pressures associated with delivery to accelerating markets, such as 5G, artificial intelligence (AI), and high-performance computing (HPC).

Jung Yun Choi, Vice President of Foundry Design Technology Team at Samsung Electronics, said: “Coupling noise between multi-die and package causes unexpected performance issues, and addressing 2.5D-IC system problems at later design stages is more difficult as design complexity increases.

“Samsung Foundry’s MDI design flow, which integrates analysis and implementation for early-stage system-level pathfinding, enables our customers to overcome performance issues and achieve cost-efficient 2.5D-IC products. Through our collaboration, customers can pull in their schedule and achieve a performance-driven product while reducing turnaround time for problem-solving.”

Key products and features of Synopsys’ Fusion Design Platform and Custom Design Platform supporting Samsung Foundry’s 7LPP 2.5D-IC MDI include:

- Fusion Compiler RTL-to-GDSII solution: Fully-automated silicon interposer routing, optimal automated placement and routing among microbumps, TSVs, and C4 bumps.

- IC Compiler II place and route: Comprehensive support for interposer creation, inter-die placement and routing, and interposer channel and power routing.

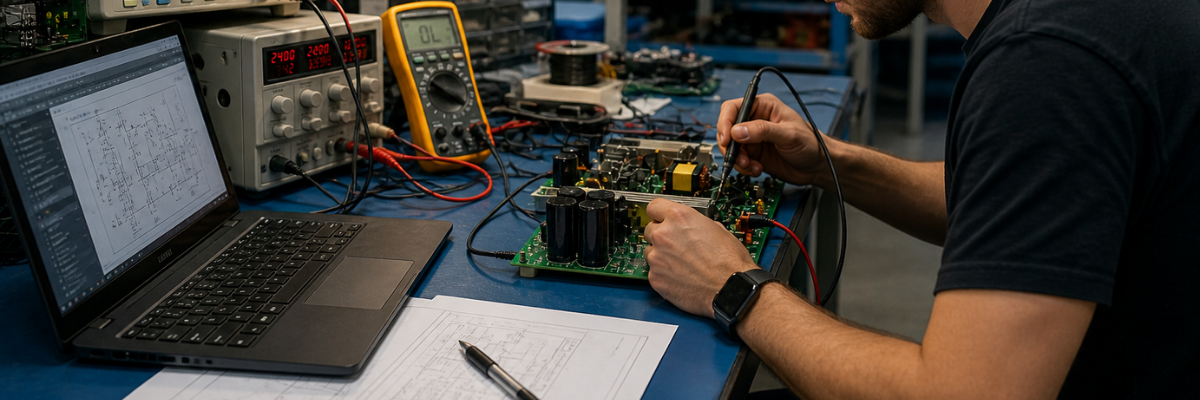

- RedHawk Analysis Fusion In-Design EM/IR: Seamless In-Design EM/IR analysis of multi-dies and silicon interposer, robust power delivery network design through cleaning missing via, open and short net correlated with ANSYS RedHawk signoff analysis.

- Custom Compiler design environment: Easy configuration setup based on powerful schematic view and auto SPICE deck generation for power and signal integrity analysis of HBM and high-speed interface (HSI) channels.

- HSPICE signal integrity analysis: Linear, transient, and StatEye analysis for PCIe Gen4.

- FineSim power and signal integrity analysis: AC and transient analysis for power integrity, crosstalk, jitter, and SSO analysis for HBM.

“With increasing interest in multi-die integration for accelerating markets such as AI, HPC, and 5G, customers need new solutions because traditional manual design doesn’t adequately address the latest power and signal noise challenges,” added Michael Sanie, Vice President of Marketing and Strategy for the Synopsys Design Group. “Synopsys’ design solutions make a multi-die integration design environment easier and more efficient, and help Samsung Foundry customers deliver faster and higher-performing 2.5D-IC products.”