At the 2018 IEEE International Electron Devices Meeting (IEDM), imec, the research and innovation hub in nanoelectronics and digital technologies, presented the first power-performance-area comparison between SRAM- and SST-MRAM-based last-level caches at the five nanometer node.

The analysis, based on design-technology co-optimization and silicon verified models, reveals that STT-MRAM meets the performance requirements for last-level caches in the high-performance computing domain. Moreover, for larger memory densities, significant energy gains are found for SST-MRAM compared to SRAM.

The increased complexity of CMOS transistor processing has led to the limited scaling of high-density SRAM cells at advanced technology nodes. STT-MRAM has emerged as a promising candidate for replacing the SRAM-based last level cache memories for systems with reduced area and energy. The core element of an STT-MRAM device is a magnetic tunnel junction in which a thin dielectric layer is sandwiched between a magnetic fixed layer and a magnetic free layer. Writing of the memory cell is performed by switching the magnetization for the free magnetic layer, by means of a current that is injected into the magnetic tunnel junction.

Imec analyzed the feasibility of introducing STT-MRAM at the five nanometer technology node for the high-performance computing domain. In a first step, a design-technology co-optimization (DTCO) was performed to define the requirements and specifications for SST-MRAM cells at the five nanometer node. Imec concluded that a high-performance 2 Perpendicular-to-Plane (CPP) STT-MRAM bit cell (with MRAM pitch being twice the contacted gate pitch (CPP) of 45nm) is the preferred solution for last-level caches at five nanometer, using 193 immersion single patterning lithography, resulting in lower technology cost.

DTCO also reveals the requirement for the current density that is needed to enable a high switching speed of the magnetic tunnel junction. For a target current density of 3.8 to 5.4mA/cm2, a resistance area product of 3.1 to 4.7Ωµm2 is required.

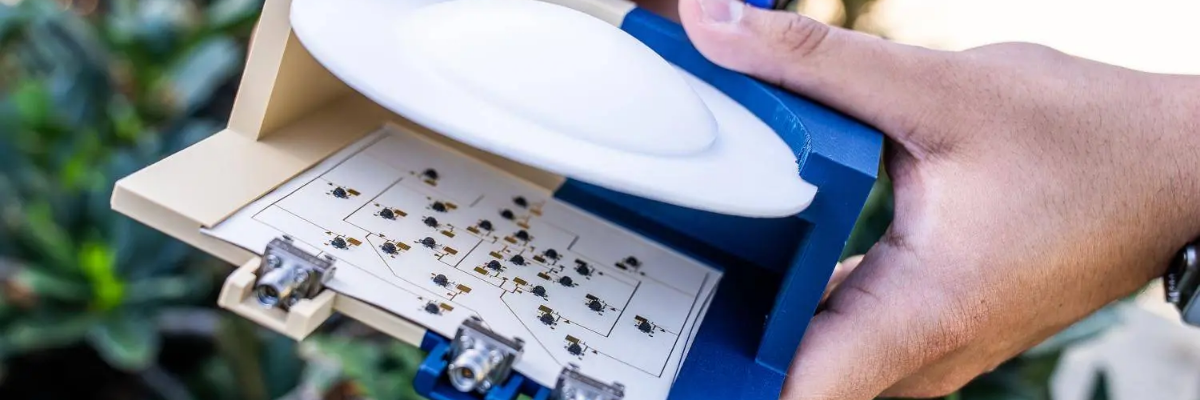

In a second step, a high-performance STT-MRAM cell was fabricated on 300mm Si wafers and the characteristics of the magnetic tunnel junction were measured experimentally. These Si verified data were then used in a model that allowed to compare the SRAM and STT-MRAM last-level cache designs for the high-performance computing domain at the five nanometer node. In these designs, the STT-MRAM cell occupies an area of 43.3% of the SRAM macro.

Gouri Sankar Kar, Program Director at imec, stated: “For the first time, DTCO and Si verified models allowed us to conclude that the STT-MRAM energy becomes more efficient as compared to SRAM for high-density memory cells (i.e., beyond 0.4MB and 5MB density for read and write operations, respectively). The comparison also reveals that the latency of the STT-MRAM is sufficient to meet the requirements of the last-level caches in the high-performance computing domain, which operate around 100MHz clock frequency.”