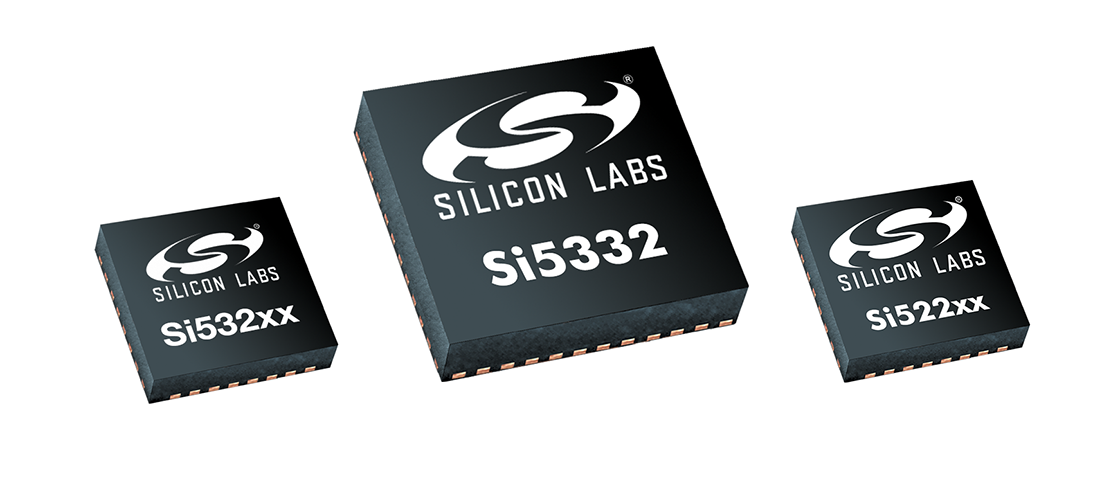

A comprehensive portfolio of timing solutions have been introduced by Silicon Labs, which provide jitter performance to meet the latest generation PCI Express (PCIe) 5.0 specification with significant design margin. The Si5332 any-frequency clock family generates PCIe Gen 5 reference clocks with jitter performance of 140 fs RMS, optimizing PCIe SerDes performance while meeting the Gen 5 specification with margin.

The Si5332 clocks generate any combination of PCIe and general-purpose frequencies, enabling clock tree consolidation across a broad range of applications.

Silicon Labs also offers the Si522xx PCIe clock generators and Si532xx PCIe buffer families, which are capable of providing two, four, eight, or twelve PCIe Gen 1/2/3/4/5-compliant outputs, making them an ideal fit for clocking a wide variety of PCIe endpoints in data center applications.

Increasingly, data center hardware designs including network interface cards (NICs), PCIe bus expanders and high-performance computing (HPC) accelerators are using low-power 1.5 or 1.8V supplies to minimize overall power consumption. Powered from 1.5 to 1.8V supply rails, the Si522xx and Si532xx devices are the industry’s lowest power PCIe clocks and buffers.

The Si522xx and Si532xx output drivers leverage Silicon Labs’ proven push-pull high-speed current steering logic (HCSL) technology, which eliminates the need for external termination resistors required by conventional PCIe clocks using constant-current output driver technology.

Silicon Labs’ new clock products are fully compliant with PCIe Gen 5 Common Clock, Separate Reference No Spread (SRNS) and Separate Reference Independent Spread (SRIS) architectures. Despite PCIe Gen 5 having more stringent jitter requirements, Silicon Labs’ new products do not require discrete power supply filtering components, simplifying PCB layout while ensuring board-level noise does not degrade clock jitter performance.

Board designers can seamlessly migrate existing PCIe Gen 1/2/3/4 designs with drop-in compatible Si5332, Si522xx and Si532xx clocks to easily upgrade existing designs to take advantage of faster PCIe serial interfaces.

“Silicon Labs is committed to providing best-in-class timing solutions to ease the migration to higher-speed PCI Express,” said James Wilson, General Manager of timing products at Silicon Labs. “Data center designers want to take advantage of PCIe Gen 5 to increase interconnect speeds between the CPU and workload accelerators, including GPUs, FPGAs and dedicated accelerator solutions. Increasing the bandwidth among networking, storage and AI resources will help enable the industry transition to 400G Ethernet.”

The Silicon Labs PCI Express clock jitter tool has been updated to include the filters necessary to accurately measure PCIe Gen 5 reference clock jitter. This software greatly simplifies PCIe clock jitter measurement, ensuring the proper filters are applied as specified by the PCI-SIG Gen 1/2/3/4/5 common clock, SRNS and SRIS specifications while providing the results in an easy-to-read format. This user-friendly utility is available at no charge at silabs.com/pcie-learningcenter.

Samples and production quantities of the Si5332 any-frequency clock, Si522xx PCIe clocks and Si532xx PCIe buffers are available now. Samples ship in two weeks and production quantities are available in four weeks. The following pricing is for 10,000-unit quantities in USD:

- Si5332 pricing ranges from $4.25 for the six output device to $4.90 for the 12-output device.

- Si522xx pricing ranges from $1.27 for the two output device to $2.76 for the 12-output device.

- Si532xx pricing ranges from $1.40 for the four output device to $2.10 for the 12-output device.

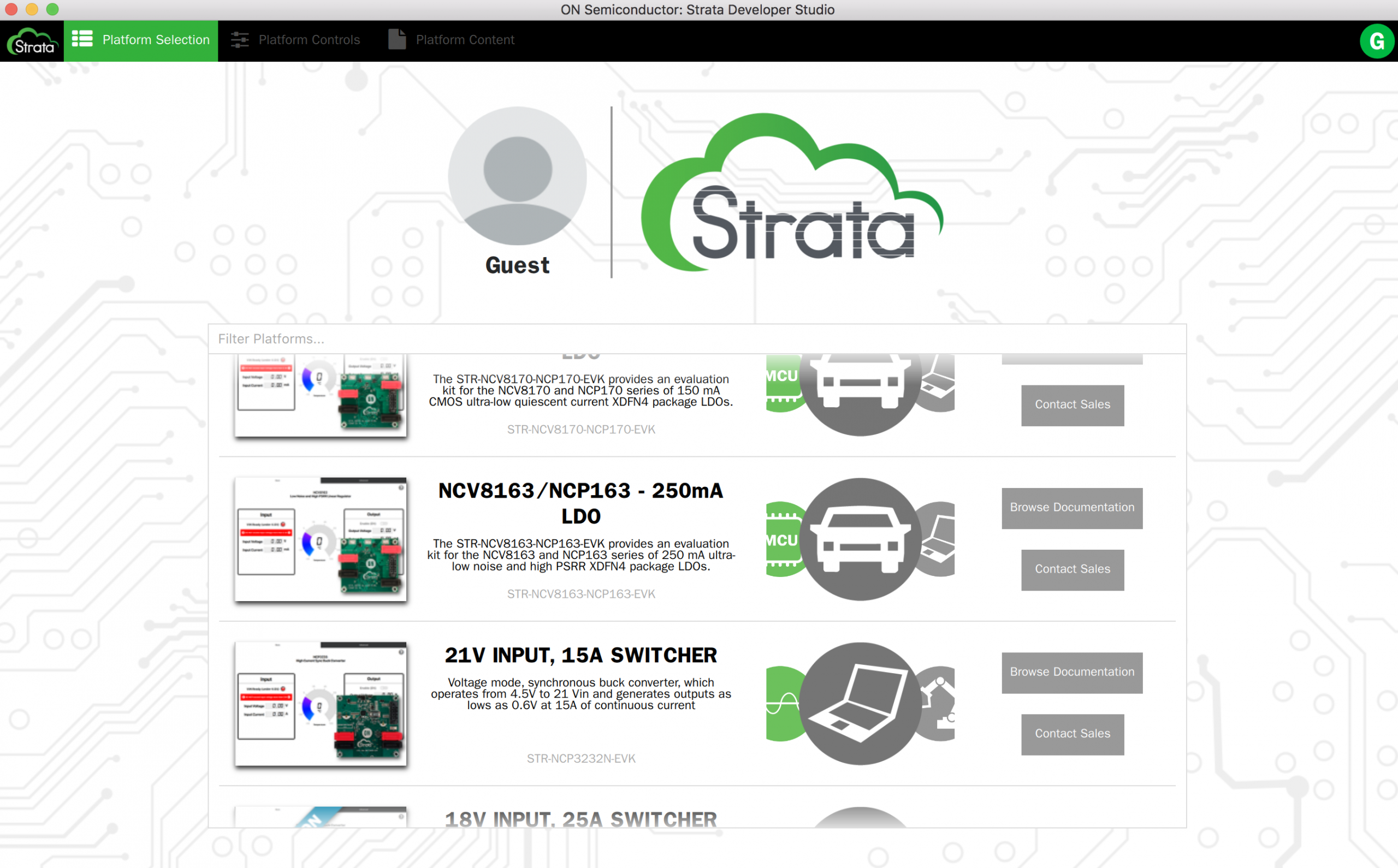

The following development kits are available to provide quick, simple product evaluations:

- Si5332 any-frequency clocks: Si5332-6EX-EVB, priced at $149 (USD MSRP).

- Si522xx PCIe clocks: Si52204-EVB, priced at $140 (USD MSRP).

- Si532xx PCIe buffers: Si53208-EVB, priced at $175 (USD MSRP).